D Flip-Flop

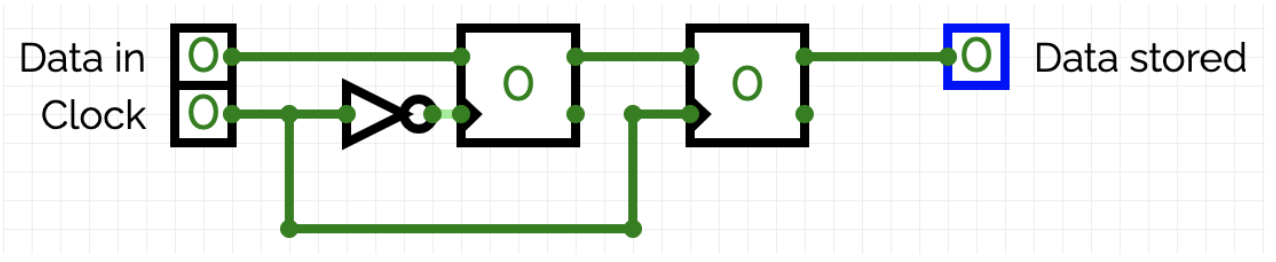

In a D-Latch, storage is controlled by Enable, making it “level-triggered”. However, for data storage, we use a D flip-flop, which is “edge-triggered”. To get an understanding of the difference between level-triggered and edge-triggered, let's implement the following circuit with two D-Latches and a NOT gate:

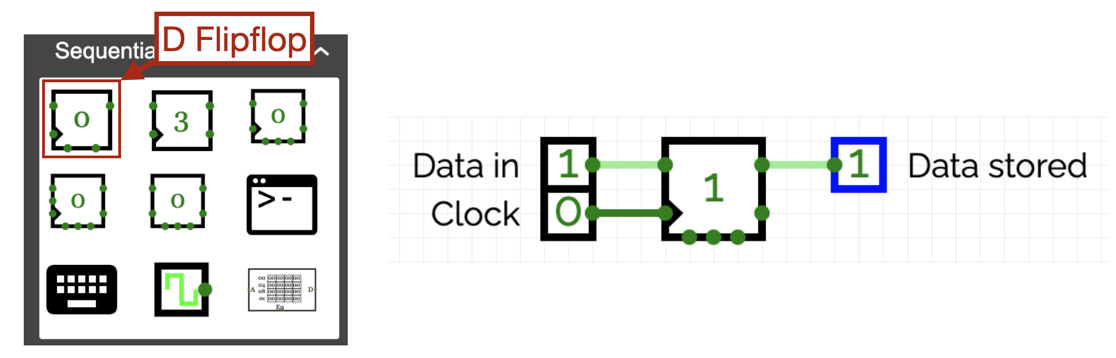

Experiment with this circuit and then explain to your neighbor (or us) why it's said that “Data in” is stored on a positive edge of Clock. Then, use a D flip-flop and confirm that it behaves the same way.